Ну чтож. Как выглядит сие чудо, мы разобрались в первой части.

Теперь можно рассказать о функциональности, которая уже есть, которая ожидается в самом ближайшем будущем и которая витает в идеях вокруг моей головы.

И так...

Есть у моего логического, так сказать, анализатора два режима (пока что): непосредственно сам Логический анализатор, и Генератор сигналов.

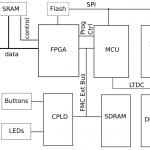

Ну начнем с первого. Для начала неплохо бы представить, как оно все устроенно, в блоках, так сказать:

Не буду шибко оригинальным, если скажу, что сделал сбор сигналов на FPGA. Я так думаю, что практически все так делают. Ну все те психи, которые, вместо того, чтобы купить готовый, собирают свой ЛА 🙂

И так — сигналы идут через входные буфера (на базе MC74HC245ADW) на шуструю SRAM (IS61LV6416L), управление которой осуществляется из FPGA (XC3S100E-4TQ144C).

FPGA тактируется кварцем в 25 МГц, из которых в самой FPGA делается уже 200 МГц. Таким образом доступ к SRAM осуществляется на скорости 200 МГц.

Это я так думал.

Но на самом деле, реально там не 200 МГц а чуток поменьше, что то в районе 100 МГц, точно не мерял, потому как пока там сигнал WE установится, пока там SRAM сообразит, пока WE сигнал уберется... в общем — долговато это все.

И в итоге более меннее нормальный семплинг данных в SRAM получается миниум в 90 микросекунд. Если хочется быстрее (а ведь хочется 🙂 ) то надо делать все внутри FPGA, там кажется у меня осталось еще места для организации небольшоно буфера, но пока до этого руки не дошли.

Воот. Таким образом имеем следующую схему:

- MCU говорит (через регистры), сколько данных с каким таймингом собирать.

- FPGA снчала «собирает» данные в SRAM.

- По окончании сбора вывешивается флаг в регистре статуса о том, что данные есть.

- MCU начинает читать регистры данных, которые маппируются на SRAM, т.е. FPGA «переводит» процесс чтения внешней шины MCU в сигналы управления SRAM.

- По окончании вычитки данных с SRAM, MCU «говорит» FPGA начать процесс заново.

- MCU рисует данные на экране.

- MCU обрабатывает ввод пользователя с кнопариков, и говорит CPLD-е, какие лампочки зажечь.

Вот собственно и весь процесс.

Немного по хардверной архитектуре, или как там оно по научному называется.

FPGA и CPLD (для чтения ввода пользователя и моргания лампочками) висят на внешней шине проца, поэтому надо разграничивать по времени обращение к ним по очереди. Так же надо разграничить по времени и обновление экрана. Объясню, почему:

Экран не мелкий: 480 х 272 пикселей. У меня еще используются два слоя (в формате ARGB8888). Они рендерятся посредством DMA2D в общий слой (в формате RGB565, используемый дисплеем), который и выводится потом посредством LTDC на экран. Т.е. мне надо 480*272*4*2 + 482*272*2 байта — это 1307776 байт. Т.е. видео буфера лежат в SDRAM, которая висит на внешней шине. Для рендеринга я использую DMA2D, это тот же DMA, только с графическим уколном, может заливать целые области определенным цветом, и конвертировать форматы изображения туда обратно.

Ключевое тут именно то, что это DMA, т.е. работа идет без использования проца, а проц тем временем может заняться чем то другим, например почитать данные из FPGA.

Но вот незадача, ST не воткнули (либо криво воткнули, я точно не узнавал) арбитра доступа к шине для DMAшек. А их там целых три DMA1, DMA2 и DMA2D.

И вот этим арбитром пришлось выступить самому процу, точнее, программе, которая на нем крутится. Если этого не делать, то на экране появляется снег, а потом проц падает в Hard Fault так как в SDRAM у меня так же и куча (HEAP в простонародии) лежит, и из нее, из-за таких вот финтов, читается мусор иногда.

Ну вот собвтенно с частью Логического анализатора более меннее разобрались.

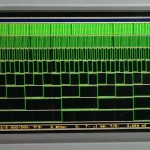

Вот еще пару картинок с некоторыми настройками по теме:

Выставление числа каналов для отображения. Максимум 16, по числу разрядов шины SRAM.

Выставление параметров семплинга и зумминга

Выставление параметров триггера.

Курсоры, информация по позиции курсоров, частота и время между курсорами.

В окошке внизу кнопочками можно выбрать курсоры для перемещения либо выключить совсем.

Большая часть этих экранных кнопочек дублируется аппаратными кнопочками и крутилками, но не все. Еще в процессе доделки.

Так же есть главное меню во всей системе для смены режимов:

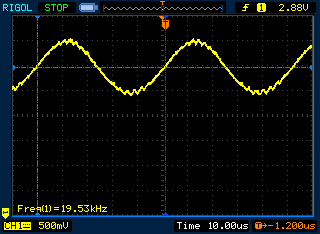

И сменяется пока что режим ЛА на режим генератора сгналов синусных

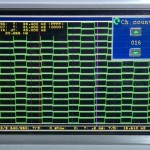

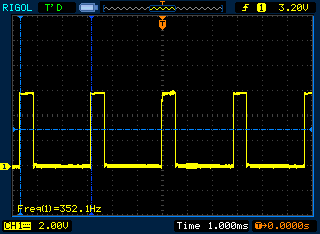

И генератор сигналов импульсных:

В принципе, если в режиме синуса выключить фильтр, то получим тот же импульсник, но с переменной скважностью.

Я заложил для генератора сигналов два канала, и на оба канала поставил отключаемый операционный усилитель, и RC фильтр. Причем с разными параметрами на двух каналах. На первом канале фильтрует слабее, чем на втором, но и соответственно амплитуда на втором ниже чем на первом, но на втором глаже получается синус, чем на первом — «ёлочкой» 🙂

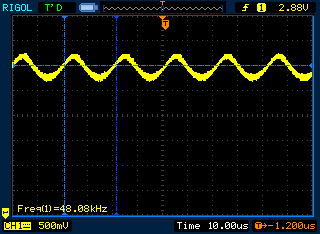

В принципе — 48 КГц, это все, что можно получить на этом генераторе синуса. Не густо, но хоть что то 🙂

В генераторе импульсов ОУшка тоже вности свои свойства в сигнал.

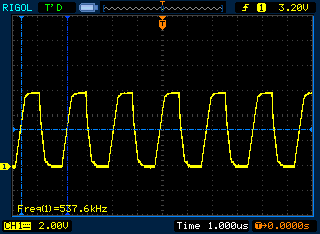

Чем быстрее частота, тем более сглаженный сигнал получается:

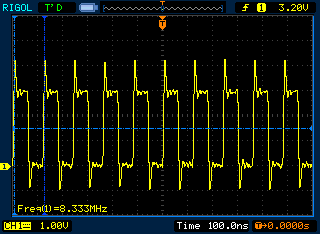

Но если отключить ОУ, то максимум, что можно получить — это 8.3 МГц

Но при такой частоте диапазон скважности довольно мал — от 0 до 5-ти (Period на картинке):

Причем при установке частоты в скобочках под словом Freq стоит расчетная якобы реальная частота, которую расчитываю я по формуле из даташитки на проц. так вот — тут стоит 10 МГц, а в реале — 8.3 МГц.

Вот как то так.

В общем — получился себе такой малобюджетный генератор и анализатор в одном флаконе.

Есть идея приделать к нему синтезатор DDS AD9850. Он уже заказан и выслан в мою сторону, так что скоро должен прийти. А приделывать я его буду хитрым образом 🙂 повешу на входные линии.

А все потому, что я при проектировании входной части использовал буфер на базе MC74HC245ADW, направлением сигнала которой так же управляет FPGA.

И есть еще один буфер для управляющих сигналов 4 в одну и 4 в другую сторону. Так что теоретически должна получиться хорошая приставка на два канала довольно приличного генератора сигналов любой сложности.

Ведь форму сигнала можно чрез FPGA сначала загнать в SRAM, а потом уже ее использовать как паттерт для генерации через DDS. Вот такая идея на ближайшее будущее 😉

Ну а на немного дальнее будущее, если будет у меня еще желание — осуществить свою дааавнюю мечту, с которой собственно вся эта канитель и началась — свой осциллограф :). Так же в форме приставки к этому ЛА через эти же входы-выходы пробников.

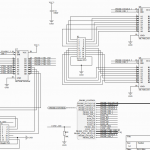

Вот схемка входной части, чтобы было более менее понятно, что я имею ввиду:

Ну пока, я думаю, на этом все. Не знаю, когда опять чего напишу, но надеюсь, что не шибко долгим будет перерыв. Идей много, дел тоже много, не везде успеваю, так что... заходите периодически, мож чего нового и объявится.

Можно еще на RSS тут где то вверху подписаться. Вроде как тоже работает.

Ну... До скорого!

Всем оптимизма! Пока!

AVR Deices – конструкции на микроконтроллерах AVR и не только…

AVR Deices – конструкции на микроконтроллерах AVR и не только…

Leave a Reply

You must be logged in to post a comment.